1. Pendahuluan[kembali]

Dalam dunia digital dan sistem logika, pengolahan serta pemilihan sinyal menjadi aspek penting dalam desain rangkaian elektronik. Salah satu komponen yang sangat vital dalam hal ini adalah multiplexer, khususnya Four-Input Multiplexer atau MUX 4:1. Komponen ini berfungsi untuk memilih satu dari empat masukan data digital berdasarkan kombinasi dua sinyal selektor, lalu meneruskan sinyal yang dipilih ke output. Dengan kata lain, multiplexer bertindak seperti saklar elektronik yang sangat efisien dan terprogram. Fungsinya yang sederhana namun penting ini membuat multiplexer banyak digunakan dalam berbagai aplikasi seperti komunikasi digital, pengolahan data, dan desain sistem tertanam (embedded systems).

Pemahaman tentang Four-Input Multiplexer menjadi sangat penting bagi mahasiswa teknik elektro maupun bidang informatika karena merupakan dasar dari sistem logika terkontrol. Dalam praktiknya, multiplexer tidak hanya digunakan untuk pengalihan sinyal, tetapi juga berperan dalam proses pengkodean data, penghematan penggunaan jalur data, dan pembuatan sirkuit logika kompleks yang lebih efisien. Dengan mempelajari cara kerja dan implementasi multiplexer, pelajar dapat mengembangkan kemampuan dalam merancang sistem logika digital yang optimal, yang nantinya sangat berguna dalam dunia industri dan riset teknologi.

2. Tujuan[kembali]

1.Memahami prinsip kerja dari Four-Input Multiplexer (MUX 4:1) dalam sistem logika digital.

2.Mengetahui cara kerja sinyal selektor dalam memilih salah satu dari empat input untuk diteruskan ke output.

3.Meningkatkan kemampuan dalam merancang dan mengimplementasikan rangkaian multiplexer menggunakan logika dasar.

4.Mengembangkan keterampilan analisis terhadap alur data dan kontrol sinyal dalam sistem digital.

5.Mampu mengaplikasikan multiplexer dalam berbagai sistem seperti komunikasi digital, pemrosesan data, dan kontrol perangkat

3. Alat dan Bahan[kembali]

GERBANG AND

4. Dasar Teori[kembali]

Gambar 9-21(a) menunjukkan diagram logika untuk 74ALS151 (74HC151) multiplexer delapan-input. Multiplexer ini memiliki input enable (ditandai dengan E̅) dan menyediakan dua output, yaitu output normal dan output invers (kebalikan).

Multiplexer 74ALS151 (juga dikenal sebagai 74HC151) adalah komponen logika digital yang berfungsi untuk memilih salah satu dari delapan input data (I₀ hingga I₇) dan mengarahkannya ke output tunggal Z. Komponen ini memiliki tiga pin selektor yaitu S₂, S₁, dan S₀ yang digunakan untuk menentukan input mana yang akan dipilih. Multiplexer ini termasuk jenis 8-to-1, artinya dari delapan input hanya satu yang dapat diteruskan ke output dalam satu waktu, tergantung pada kombinasi dari ketiga pin selektor tersebut.

Salah satu fitur penting dari IC ini adalah adanya input enable (E̅), yang berfungsi sebagai pengontrol aktif atau tidaknya multiplexer. Ketika E̅ berada dalam kondisi LOW (0), multiplexer akan aktif dan memilih salah satu dari delapan input berdasarkan kombinasi S₂S₁S₀ untuk diteruskan ke output Z. Selain output Z, IC ini juga menyediakan output kebalikannya (inversi), yaitu Z̅, yang merupakan komplement dari nilai Z.

Namun, saat input enable E̅ bernilai HIGH (1), multiplexer akan dinonaktifkan. Dalam kondisi ini, tidak peduli berapa pun nilai dari input selektor atau data inputnya, output Z akan selalu bernilai 0, menandakan bahwa tidak ada data yang dipilih atau diteruskan. Dengan fitur ini, IC 74ALS151 dapat digunakan dalam sistem digital yang memerlukan pengaturan dan pemilihan data secara terkontrol dan selektif, terutama dalam aplikasi pemrosesan sinyal dan pengalihan data.

5. Percobaan[kembali]

a) Prosedur[kembali]

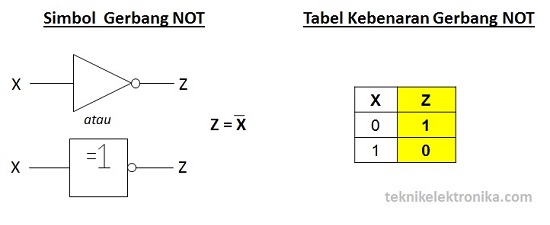

Rangkaian pada gambar merupakan implementasi logika dari 74ALS151, yaitu sebuah multiplexer 8-to-1 yang dibangun menggunakan gerbang logika dasar seperti NOT, AND, dan OR. Multiplexer ini memiliki delapan input data (D0 hingga D7), tiga input selektor (S2, S1, S0), dan satu input enable (E̅). Fungsi utama dari rangkaian ini adalah untuk memilih salah satu dari delapan input data berdasarkan kombinasi tiga bit selektor, dan mengarahkannya ke satu output tunggal, yaitu Z.

Tiga input selektor (S2, S1, S0) digunakan untuk menentukan input data mana yang akan diteruskan ke output. Untuk menghasilkan kombinasi pemilihan yang tepat, sinyal dari selektor ini diproses terlebih dahulu melalui gerbang NOT agar dapat membentuk semua kombinasi biner dari 000 hingga 111. Hasil dari proses ini kemudian masuk ke delapan buah gerbang AND, di mana masing-masing gerbang AND mewakili satu jalur pemilihan input (D0 hingga D7). Hanya satu gerbang AND yang akan aktif dalam satu waktu, yaitu yang sesuai dengan kombinasi input selektor.

Setelah sinyal data dipilih melalui gerbang AND yang aktif, sinyal tersebut diteruskan ke gerbang OR besar yang menggabungkan semua keluaran dari delapan gerbang AND. Karena hanya satu jalur yang aktif, maka output dari gerbang OR akan sama dengan nilai dari input data yang dipilih. Jika input enable (E̅) bernilai tinggi (1), maka seluruh jalur akan dinonaktifkan sehingga output Z akan bernilai 0, tidak peduli berapa pun nilai input selektor atau data. Dengan demikian, rangkaian ini bekerja sebagai pemilih data yang terkontrol oleh input enable dan input selektor secara sistematis.

b) Rangkaian simulasi [kembali]

c) Video Simulasi [kembali]

.png)

.png)

Tidak ada komentar:

Posting Komentar